Soft 6502 Second Processor Guide

Use - General |

↖ |

The Soft 6502 Second Processor provides the logic to turn your hardware development board into an Acorn 6502 Second Processor.

The currently supported development boards are :

| Board | Clock | Bench | I/O |

|---|---|---|---|

| (click link for info) | (MHz) | (MHz) | (Volt) |

| Terasic DE1 | 40 | 40 | 3.3 (*1) |

| Terasic DE0 Nano | 80 | 156 | 3.3 |

| Terasic Cyclone V GX Starter Kit | 100 | 198 | 3.3 |

| Terasic DE0 Nano SOC | 100 | 198 | 3.3 |

| Altera Stratix III FPGA Development Kit | 110 | 226 | 2.5 |

| Terasic DE10 Lite | 80 | 156 | 3.3 |

| Altera Stratix V Advanced Systems Development Kit | 180 | 384 | 2.5 |

| Terasic DE10 Nano | 90 | 186 | 3.3 |

| Terasic Cyclone 10 LP Evaluation Kit | 80 | 156 | 3.3 |

'Clock (MHz)' indicates the highest clock speed that the soft Second Processor will run at. It will also run at any lower, integer clock speed, including the original ones (3 or 4 MHz).

'Bench (MHz)' indicates the 'benchmark' speed at the highest clock speed. On an original Second Processor, this would equal the clock speed. On the soft one, it is roughly two times the clock speed, if the board uses my own 65C02 core (which executes instructions in far less cycles than a real 65C02).

'I/O (Volt)' indicates the I/O voltage of the development board. Since the Tube I/O voltage is 5, a converter like TubeSilencer is required to avoid damaging the development board.

Note (*1) : The Terasic DE1 can also be connected directly to the Tube, because its I/O pins are 5V tolerant. But it is nevertheless recommended to use a converter like TubeSilencer.

Before you continue, please note that doing anything described here is at your own risk !

Your Acorn machine's Tube interface may be connected to your development board in two different ways, designated as '20-pin' and '40-pin', both involving a TubeSilencer.

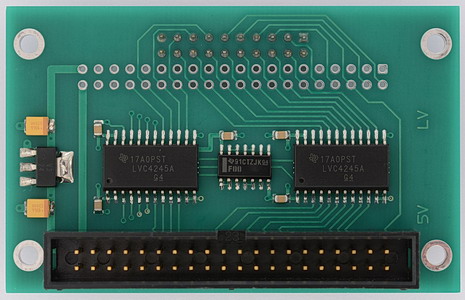

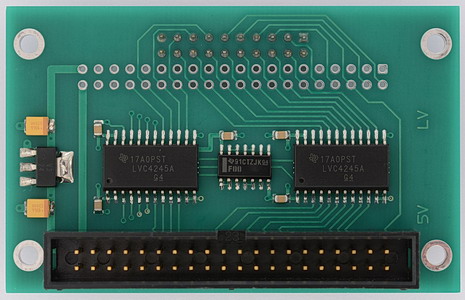

Note that the 'in' and 'out' connectors on TubeSilencer are marked by '5V' and 'LV' respectively, at the pin 1 side. Your machine connects to the 'in', your development board to the 'out'.

The 20-pin way allows connection via a 20-pin TubeSilencer. The TubeSilencer is plugged directly into the exact middle of the relevant 40-pin development board socket. I.e. this works out as : from 40-pin Tube socket, via 40-wire straight cable, via 20-pin TubeSilencer, to 40-pin development board socket.

So, a 20-pin interface looks like this :

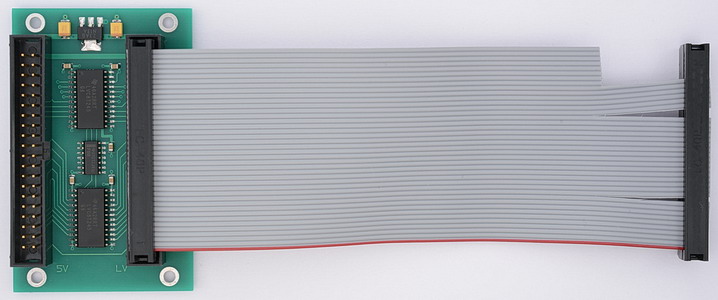

The 40-pin way allows connection via a 40-pin TubeSilencer. The TubeSilencer is connected to the relevant 40-pin development board socket via a specially cut-up 40-wire cable. I.e. this works out as : from 40-pin Tube socket, via 40-wire straight cable, via 40-pin TubeSilencer, via 40-wire specially cut-up cable, to 40-pin development board socket. The Terasic DE1 (only) may also be connected like this : from 40-pin Tube socket, via 40-wire specially cut-up cable, to 40-pin development board socket (although using a TubeSilencer is still recommended).

So, a 40-pin interface looks like this :

The specially cut-up cable is wired as follows (TS = TubeSilencer, DB = development board) :

| TS side pins | DB side pins |

|---|---|

| 1 through 10 | 1 through 10 |

| 11 through 26 | 12 through 27 |

| 27 through 32 | 30 through 35 |

| 33 through 40 | not connected |

The cable can be fabricated quite easily from two 40-pin IDC connectors and a short piece (10 cm or so) of 40-wire flatcable, as follows :

Proceed as follows :

Using the soft 6502 Second Processor is, in general, no different than using the real one, so please refer to the relevant manuals (if you don't have them, try Internet).

However, on the soft one you can change the processor clock frequency to any whole number of MHz (50 MHz in the examples below). The transition to the new frequency is seamless, and survives (CTRL-)BREAK. Note that the maximum frequency (see table above) is automatically selected if you attempt to exceed it, and that 0 selects the default frequency (4 MHz).

There are two ways to switch :

The 'slow' 65C02 core that is used on a few boards is '(C) Arlet Ottens, arlet@c-scape.nl' and '(C) 2016 David Banks and Ed Spittles'.

All other logic design, including the 'fast' 65C02 core and the Tube ULA, is my own.